PCI之撸起袖子加油干

thedairygame

2020.12.04 星期五 晴

PCI之继续干!

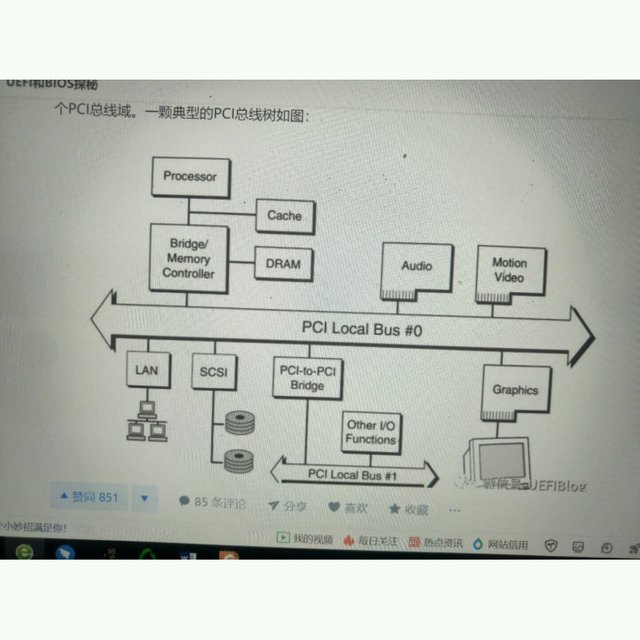

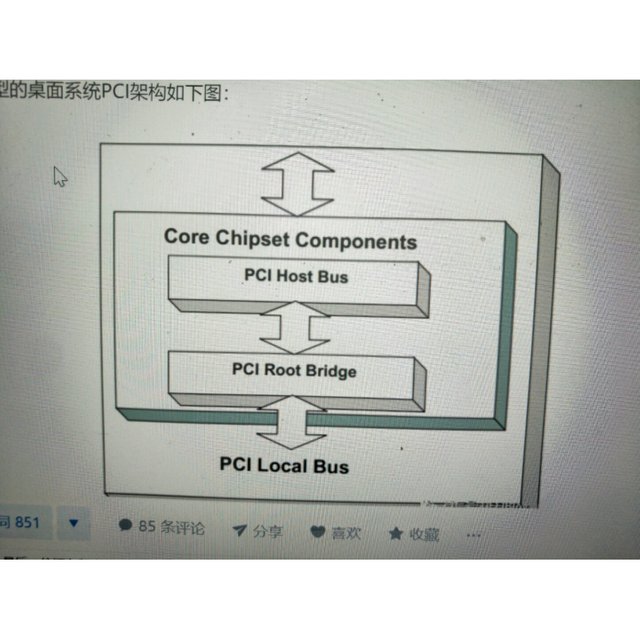

昨天说了PCI的系统总线,今天说一说PCI的本地接口总线,也就是接CPU的接口。

本地总线接口的信号为:

CCS#:表面意思是是否选择PCI 9054的寄存器(应该是某个选择作用的寄存器,LCS?)。但我看官方demo进行上拉了,10k上拉。

LCLK:本地总线的时钟信号,串一个22或33欧姆的小电阻,可以提高信号质量。

LEDon/LEDin:此引脚作为输出,连接LED指示板卡热插拔情形,作为输入,指示板卡的锁定状态。就是控制LED状态。至于锁定状态或许指的就是插槽状态,是否插入的问题。

LINT#:本地中断引脚。10k上拉。

LRESETo#:本地总线复位信号输出。10k上拉。

MODE[1:0],模式选择,如果为00,则是C模式,即LOCAL端的地址线和数据线分开,如果是01,则是J模式,则LOCAL端的地址/数据总线复用,如果为11,则为M模式,M模式针对Motorola的MPC850/860而设计。C相对来说比较简单。

USERi:用户自定义输入,可由寄存器读取。这个引脚还可用作DACK0#的用法,表示DMA数据传输被执行(DMA响应信号),低电平有效。此引脚还有一种用法,就是本地锁定信号输入LLOCKi#。表示此操作是一个原子操作(atomic),不可被打断,不可被颠倒,需要多个传输周期。用于PCI总线Initiator的直接本地访问(😱)。

USERo:用户自定义输出,可由寄存器控制输出。这个引脚还可用作DMA传输请求信号DREQ0#以及标志着一个PCI Target操作(LLOCKo#),数据从PCI到LOCAL的传输的原子操作,或许是这样吧!

以上是本地总线与CPU的一些接口信号。以下是PCI 9054的模式接口,由于C模式最简单,以C模式为研究对象。

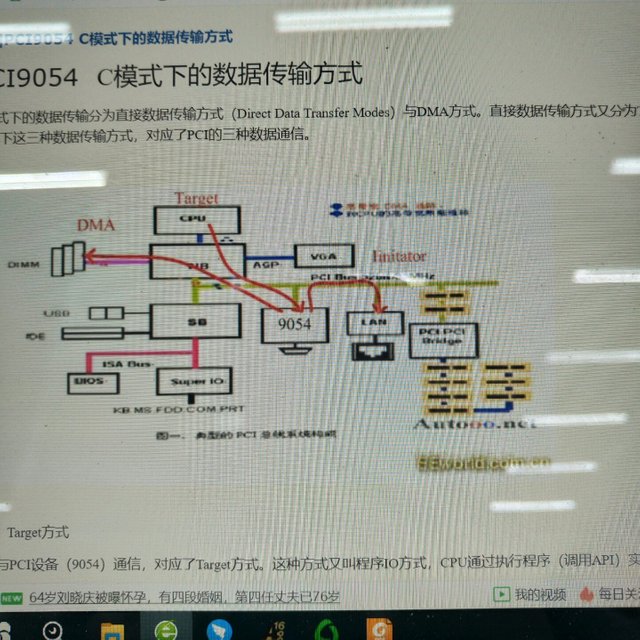

C模式下有3种数据传输方式,Target,是CPU与PCI设备间的通信,Initator是PCI设备间的通信,DMA是PCI与主存间的通信。

C模式下的接口引脚为:

ADS#,地址选通信号,指示着新的总线访问的地址信号的起始。所有总线上的信号都在监控ADS#是否有效。一旦ADS#有效,它们将会做一些相应的动作,如奇偶检查,协议检查,地址译码等。

BIGEND#引脚,是否使用大端字节序传输数据。大端字节序(BIGENDIAN)认为第一个字节是最高位字节,小端字节序认为第一个字节序是最低位字节,一般来说,x86系列CPU是小端字节序,PowerPC是大端字节序,网络字节序也是大端字节序。由于这里用的是x86 Windows系统,采用小端字节序,使用上拉电阻接高电平(3.3V)。

BLAST#信号,在本地总线操作中,BLAST#信号是用来截止操作的,如果在传输第一个字节的时候,将BLAST#信号置有效,就只传送一个字节,否则BLAST#信号一直无效,直到传送完最后一个字节以后(还是当时?),将BLAST#置有效,停止突发传输。

BREQi:输入,总线申请信号,LOCAL主机申请总线时有效。当通过配置寄存器使能该位后,PCI9054将要在两个LWORD周期内,释放本地总线。也许此时总线处于Target模式或DMA模式,而总线需要执行Initator操作。

BREQo:表明9054在Initator操作时需要执行一个Target操作。与BREQi一样,官方demo里是下拉,但公司设置的是上拉。这应该不重要吧?

BTERM#信号:双向,突发终止。作为输入,有效时9054停止传输。传输没有完成时,9054产生一个新的地址周期并继续传输。作为输出,检测到PCIE异常中断信号时,9054使能BTERM#去要求主机终止当前传输。

DMPAF信号:默认功能,Initator操作下,写FIFO满输出标志。此引脚也可用作EOT#信号输入,在DMA通道已经激活了的情况下,用来终止当前的DMA传输。

DP[3:0],双向,数据校验信号,对总线的四字节通道数据进行校验。这个可以悬空不用。但是怎么用确实也是个问题。

LA[31:2],双向,本地地址总线,提供总线物理地址的高30位。突发模式时,地址会自动累加。

LBE[3:0]#,双向,本地字节使能,利用此信号可实现32位,16位和8位数据传输,同时由该管脚提供辅助增加的地址信号。

LD[31:0],双向,本地数据总线,为LOCAL总线主控时(Target),可以传输8位,16位或32位数据;直主模式访问(Initator?)必须32位数据传输。

LHOLD:输出,本地总线独占请求信号。

LHOLDA:输入,本地总线独占应答信号。

LSERR#:输出,本地系统错误中断输出信号。

LW/R#:本地读写信号。

READY#:双向,IO就绪信号。直从(Target)或DMA下为输入,直主下为输出,表明可读数据代写数据已经在下个时钟上升沿到达前准备好。

WAIT#:IO,在本地总线插入等待状态。

通常高电平有效的接下拉电阻,低电平有效的接上拉电阻。但本地地址总线全部设置成了上拉。

9054以及PCI总线的模式多,概念多,信号也有点多,到此为止,感觉有些细节仍比较糊涂。但先这样吧!

然后,继续精进。

[WhereIn Android] (http://www.wherein.io)

This post has been rewarded by the Steem Community Curation Project #wherein 我是谁?你又是谁?!我为什么会在这里?你加了cnsteem 没?!

This post has been rewarded by #nutbox. Nutbox is the DApp Incubator of Steem , and you can mine PNUT token by staking to us via https://nutbox.io .Contact us at https://discord.gg/zPkMuGY